Introduction

IC (Integrated Circuit) Design & Verification tools are specialized software platforms used to design, simulate, validate, and prepare semiconductor chips for manufacturing. In simple terms, these tools help engineers create everything from microprocessors and GPUs to custom ASICs and SoCs with precision and reliability.

In today’s hardware-driven world, IC complexity is growing exponentially due to AI workloads, automotive electronics, 5G infrastructure, and IoT expansion. This makes robust design and verification workflows essential—not just for performance, but also for power efficiency, reliability, and security. Modern IC tools now incorporate AI-assisted automation, cloud-based simulation, and early-stage verification to reduce costly design errors.

Common use cases include:

- Designing ASICs and SoCs for AI, mobile, and embedded systems

- Functional and formal verification of digital designs

- Analog and mixed-signal circuit simulation

- Timing, power, and signal integrity analysis

- RTL-to-GDSII design flows for chip manufacturing

Key evaluation criteria for buyers:

- Digital, analog, and mixed-signal design capabilities

- Verification depth (functional, formal, timing, power)

- Performance for large-scale chip designs

- AI-assisted automation features

- Integration with foundries and IP ecosystems

- Ease of use and onboarding complexity

- Deployment flexibility (cloud vs on-premise)

- Security and IP protection mechanisms

- Vendor support and ecosystem maturity

Best for: Semiconductor companies, chip designers, hardware engineers, and R&D teams working on ASIC, FPGA, and SoC development across industries like automotive, telecom, AI, and consumer electronics.

Not ideal for: Non-specialized teams or those working only on basic PCB-level designs. For simpler workflows, PCB-focused EDA tools are more appropriate.

Key Trends in IC Design & Verification Tools for 2026 and Beyond

- AI-driven verification and optimization: Machine learning is increasingly used to detect bugs, optimize timing, and improve layout efficiency.

- Shift-left verification strategies: Verification is happening earlier in the design cycle to reduce late-stage failures.

- Cloud-native simulation environments: High-performance simulations are moving to scalable cloud infrastructure.

- Chiplet and heterogeneous integration: Tools are evolving to support modular chip design approaches.

- Formal verification adoption: Growing reliance on mathematical proofs for correctness in safety-critical systems.

- Hardware security integration: Built-in capabilities to detect vulnerabilities and ensure secure design practices.

- Integration with software workflows: Closer alignment with CI/CD pipelines and DevOps practices.

- Open-source IC design movement: Increasing interest in tools like OpenROAD for cost-efficient design.

- Advanced node support: Tools optimized for sub-5nm and emerging semiconductor processes.

- Collaborative design environments: Improved support for distributed engineering teams.

How We Selected These Tools (Methodology)

The tools in this list were selected using a structured evaluation approach:

- High industry adoption and recognition among semiconductor companies

- Comprehensive feature coverage across IC design and verification workflows

- Proven reliability in handling complex chip designs

- Performance benchmarks for large-scale simulations

- Strong integration with foundries, IP vendors, and manufacturing ecosystems

- Availability of APIs and automation capabilities

- Vendor support quality and ecosystem maturity

- Suitability across different company sizes and use cases

- Alignment with modern trends such as AI and cloud computing

- Documentation quality and community support

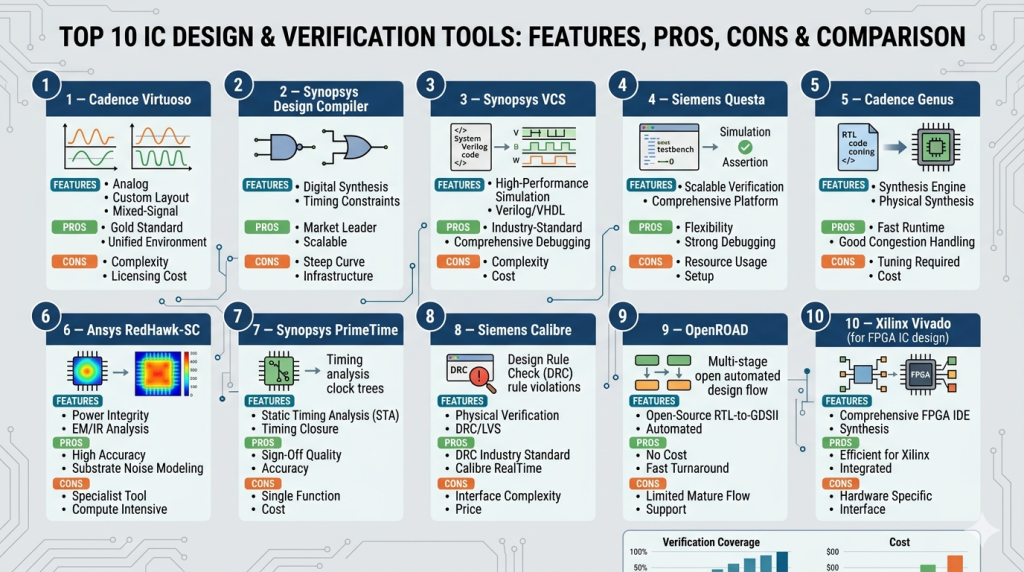

Top 10 IC Design & Verification Tools Tools

#1 — Cadence Virtuoso

Short description: A leading platform for analog, mixed-signal, and custom IC design, widely used in advanced semiconductor development.

Key Features

- Analog and mixed-signal design environment

- Custom layout and schematic tools

- Simulation integration (Spectre)

- AI-assisted design optimization

- Advanced node support

- Layout-versus-schematic (LVS) verification

Pros

- Industry-standard for analog design

- Strong integration across Cadence ecosystem

Cons

- Complex learning curve

- Expensive licensing

Platforms / Deployment

Linux

Self-hosted / Hybrid

Security & Compliance

Not publicly stated

Integrations & Ecosystem

Cadence Virtuoso integrates deeply with simulation and verification tools.

- Spectre simulation engine

- Integration with Cadence digital tools

- Foundry PDK compatibility

- Scripting via SKILL language

Support & Community

Strong enterprise support with extensive training resources.

#2 — Synopsys Design Compiler

Short description: A widely used synthesis tool for converting RTL designs into gate-level implementations.

Key Features

- RTL-to-gate synthesis

- Timing and power optimization

- Multi-voltage and low-power design support

- Integration with verification tools

- Advanced node support

Pros

- Industry-standard synthesis engine

- High-performance optimization

Cons

- Complex configuration

- Expensive for small teams

Platforms / Deployment

Linux

Self-hosted / Hybrid

Security & Compliance

Not publicly stated

Integrations & Ecosystem

- Integration with Synopsys verification tools

- Foundry compatibility

- Automation via scripting

- CI/CD pipeline integration

Support & Community

Enterprise-grade documentation and support.

#3 — Synopsys VCS

Short description: A high-performance simulation tool for functional verification of digital designs.

Key Features

- SystemVerilog simulation

- Debugging and waveform analysis

- Coverage-driven verification

- High-speed simulation engine

- Integration with verification frameworks

Pros

- Fast simulation performance

- Strong verification ecosystem

Cons

- Steep learning curve

- Licensing cost

Platforms / Deployment

Linux

Self-hosted / Hybrid

Security & Compliance

Not publicly stated

Integrations & Ecosystem

- Integration with UVM frameworks

- Debugging tools

- Automation APIs

- Verification toolchain support

Support & Community

Widely adopted with strong enterprise support.

#4 — Siemens Questa

Short description: A comprehensive verification platform supporting simulation, formal verification, and debugging.

Key Features

- Functional and formal verification

- Coverage analysis

- Debugging tools

- UVM support

- Scalable simulation

Pros

- Strong formal verification capabilities

- Scalable for large designs

Cons

- Complex interface

- Requires expertise

Platforms / Deployment

Linux / Windows

Self-hosted / Hybrid

Security & Compliance

Not publicly stated

Integrations & Ecosystem

- Integration with Siemens EDA tools

- UVM and SystemVerilog support

- APIs for automation

- Debugging ecosystem

Support & Community

Enterprise support with extensive documentation.

#5 — Cadence Genus

Short description: A modern synthesis tool for digital IC design, optimized for performance and power efficiency.

Key Features

- RTL synthesis

- Power and timing optimization

- Multi-corner analysis

- Integration with Cadence tools

- Advanced node support

Pros

- High optimization accuracy

- Strong performance

Cons

- Requires expertise

- Premium pricing

Platforms / Deployment

Linux

Self-hosted / Hybrid

Security & Compliance

Not publicly stated

Integrations & Ecosystem

- Cadence digital flow integration

- Foundry support

- Automation APIs

- Verification tool integration

Support & Community

Enterprise-level support and training.

#6 — Ansys RedHawk-SC

Short description: A specialized tool for power integrity and reliability analysis in IC designs.

Key Features

- Power integrity analysis

- Electrostatic discharge (ESD) simulation

- Reliability analysis

- Multiphysics simulation

- Scalable architecture

Pros

- High accuracy for power analysis

- Essential for advanced nodes

Cons

- Not a full design tool

- Requires specialized knowledge

Platforms / Deployment

Linux

Cloud / Hybrid

Security & Compliance

Not publicly stated

Integrations & Ecosystem

- Integration with design tools

- HPC environments

- APIs for scripting

- Simulation workflows

Support & Community

Strong enterprise support.

#7 — Synopsys PrimeTime

Short description: A leading static timing analysis (STA) tool for verifying timing closure in digital designs.

Key Features

- Static timing analysis

- Multi-corner timing validation

- Power analysis

- Signoff verification

- Advanced node support

Pros

- Industry-standard STA tool

- High accuracy

Cons

- Complex workflows

- High cost

Platforms / Deployment

Linux

Self-hosted / Hybrid

Security & Compliance

Not publicly stated

Integrations & Ecosystem

- Integration with synthesis tools

- Foundry compatibility

- Automation scripts

- Verification workflows

Support & Community

Strong enterprise ecosystem.

#8 — Siemens Calibre

Short description: A widely used physical verification tool for DRC, LVS, and signoff checks.

Key Features

- Design rule checking (DRC)

- Layout vs schematic (LVS)

- Parasitic extraction

- Signoff verification

- Foundry rule integration

Pros

- Industry-standard verification

- Highly accurate

Cons

- Complex setup

- Expensive

Platforms / Deployment

Linux

Self-hosted / Hybrid

Security & Compliance

Not publicly stated

Integrations & Ecosystem

- Foundry integration

- Design tool compatibility

- Automation APIs

- Verification workflows

Support & Community

Strong enterprise adoption.

#9 — OpenROAD

Short description: An open-source toolchain for automated digital IC design, gaining traction in research and startups.

Key Features

- RTL-to-GDS flow

- Open-source architecture

- Scriptable workflows

- Integration with open PDKs

- Automated placement and routing

Pros

- Free and flexible

- Growing innovation

Cons

- Limited enterprise support

- Not suitable for all production use cases

Platforms / Deployment

Linux

Self-hosted

Security & Compliance

Not publicly stated

Integrations & Ecosystem

- Open-source toolchains

- APIs and scripting

- Academic collaborations

- PDK compatibility

Support & Community

Active open-source community.

#10 — Xilinx Vivado (for FPGA IC design)

Short description: A design suite for FPGA-based IC development, including synthesis, simulation, and debugging.

Key Features

- FPGA synthesis and implementation

- Simulation and debugging

- IP integration

- Hardware/software co-design

- Timing and power analysis

Pros

- Strong FPGA ecosystem

- Integrated workflow

Cons

- Limited for ASIC design

- Resource-heavy

Platforms / Deployment

Windows / Linux

Self-hosted

Security & Compliance

Not publicly stated

Integrations & Ecosystem

- FPGA IP libraries

- Embedded toolchains

- Simulation tools

- Hardware debugging tools

Support & Community

Large user base and strong documentation.

Comparison Table (Top 10)

| Tool Name | Best For | Platform(s) Supported | Deployment | Standout Feature | Public Rating |

|---|---|---|---|---|---|

| Cadence Virtuoso | Analog IC design | Linux | Hybrid | Mixed-signal design | N/A |

| Synopsys Design Compiler | RTL synthesis | Linux | Hybrid | High-performance synthesis | N/A |

| Synopsys VCS | Simulation | Linux | Hybrid | Fast verification | N/A |

| Siemens Questa | Verification | Windows, Linux | Hybrid | Formal verification | N/A |

| Cadence Genus | Digital synthesis | Linux | Hybrid | Optimization accuracy | N/A |

| Ansys RedHawk | Power analysis | Linux | Cloud/Hybrid | Power integrity | N/A |

| Synopsys PrimeTime | Timing analysis | Linux | Hybrid | STA accuracy | N/A |

| Siemens Calibre | Physical verification | Linux | Hybrid | DRC/LVS signoff | N/A |

| OpenROAD | Open-source IC design | Linux | Self-hosted | Free RTL-to-GDS | N/A |

| Xilinx Vivado | FPGA design | Windows, Linux | Self-hosted | FPGA ecosystem | N/A |

Evaluation & Scoring of IC Design & Verification Tools

| Tool Name | Core (25%) | Ease (15%) | Integrations (15%) | Security (10%) | Performance (10%) | Support (10%) | Value (15%) | Weighted Total |

|---|---|---|---|---|---|---|---|---|

| Cadence Virtuoso | 10 | 6 | 9 | 7 | 10 | 9 | 6 | 8.45 |

| Synopsys Design Compiler | 10 | 6 | 9 | 7 | 10 | 9 | 5 | 8.30 |

| Synopsys VCS | 9 | 6 | 9 | 7 | 10 | 9 | 6 | 8.15 |

| Siemens Questa | 9 | 6 | 8 | 7 | 9 | 8 | 6 | 7.85 |

| Cadence Genus | 9 | 6 | 8 | 7 | 9 | 8 | 6 | 7.85 |

| Ansys RedHawk | 8 | 5 | 7 | 7 | 9 | 8 | 6 | 7.30 |

| Synopsys PrimeTime | 10 | 5 | 8 | 7 | 10 | 9 | 5 | 8.10 |

| Siemens Calibre | 10 | 5 | 8 | 7 | 10 | 9 | 5 | 8.10 |

| OpenROAD | 6 | 5 | 6 | 5 | 7 | 5 | 10 | 6.65 |

| Xilinx Vivado | 8 | 7 | 8 | 6 | 8 | 8 | 7 | 7.65 |

How to interpret these scores:

- Scores are relative comparisons, not absolute measures.

- Enterprise tools excel in performance and feature depth but may score lower in value.

- Open-source tools provide strong value but may lack support and advanced capabilities.

- Use scores to shortlist tools based on your priorities.

- Always validate with real-world testing before final selection.

Which IC Design & Verification Tools Tool Is Right for You?

Solo / Freelancer

- Recommended: OpenROAD, Vivado (for FPGA)

- Focus on cost, accessibility, and flexibility.

SMB

- Recommended: Vivado, selective use of Synopsys tools

- Balance between cost and capability.

Mid-Market

- Recommended: Siemens Questa, Cadence Genus

- Need scalable verification and synthesis workflows.

Enterprise

- Recommended: Cadence Virtuoso, Synopsys Suite, Siemens Calibre

- Require full-stack IC design, verification, and signoff tools.

Budget vs Premium

- Budget: OpenROAD

- Premium: Cadence, Synopsys

Feature Depth vs Ease of Use

- Deep features: Synopsys, Cadence

- Easier workflows: FPGA tools like Vivado

Integrations & Scalability

- Strong ecosystems: Cadence, Synopsys

- Flexible/open: OpenROAD

Security & Compliance Needs

- Enterprise tools typically offer better IP protection features.

- Open-source tools require internal governance.

Frequently Asked Questions (FAQs)

What are IC design and verification tools used for?

They are used to design, simulate, and validate semiconductor chips before manufacturing.

Are these tools expensive?

Yes, enterprise tools can be very expensive. Open-source tools are free but less feature-rich.

How long does it take to learn these tools?

Learning can take weeks to months depending on complexity and prior experience.

Do these tools support cloud deployment?

Many modern tools support cloud or hybrid environments.

What is verification in IC design?

Verification ensures that the chip design behaves as intended before fabrication.

Are open-source IC tools reliable?

They are improving rapidly but may not yet match enterprise-grade reliability.

What programming languages are used?

Commonly used languages include Verilog, VHDL, and SystemVerilog.

Can these tools integrate with CI/CD?

Yes, many support automation and pipeline integration.

Is security important in IC design?

Yes, especially for protecting intellectual property and preventing vulnerabilities.

What is the biggest challenge in IC design?

Managing complexity, ensuring correctness, and meeting performance targets.

Conclusion

IC Design & Verification tools are essential for building modern semiconductor systems. As chip complexity increases, these tools enable engineers to design efficiently, verify thoroughly, and deliver reliable products.

There is no universal “best” tool:

- Enterprise teams should focus on comprehensive ecosystems like Cadence and Synopsys.

- Mid-sized teams should balance scalability and cost with tools like Siemens Questa.

- Startups and individuals can explore OpenROAD and FPGA-based solutions.